|

|

12-10: Меню Tools |

Часть 12: МЕНЮ СУММАРНО

|

|

12-10: Меню Tools |

Это меню – коллекция подменю, которые управляют разными инструментами анализа и синтеза в Electric. Для анализа есть контролер правил разработки, симулятор, множество интерфейсов симуляторов и контролер последовательности сети. Для синтеза есть трассировщики, генераторы PLA, компилятор VHDL и компилятор системы silicon размещения-и-разводки (place-and-route).

|

|

Это подменю управляет контролером правил разработки. Есть система инкрементирования, которая отслеживает всю разработку и отображает подходящие предупреждения. Есть также иерархический контролер и интерфейс системы Dracula DRC. |

|

|

Hierarchical Check |

Этим иерархически проверяется текущий фасет (проверяется вся геометрия, все пути вниз по иерархии). |

|

|

Check this Level Only |

Эта команда проверяет текущий фасет не иерархически (проверяется только геометрия текущего фасета без каких либо подфасет). |

|

|

|

|

|

|

DRC Options... |

Эта команда позволяет вам управлять количеством опций DRC, включая, будет или нет запущено инкрементирование DRC, будут ли интерактивно подсвечены ошибки и т.д.

|

|

|

DRC Rules... |

Эта команда предоставляет способ проверить и модифицировать правила разработки (используя области "For layer" и "To layer").

|

|

|

Clear Ignored Errors |

Эта команда говорит контролеру правил разработки очистить список игнорируемых ошибок, которые могут накапливаться. |

|

|

|

|

|

|

Write Dracula Deck |

Эта команда говорит контролеру правил разработки произвести входную деку для контролера правил разработки Dracula. В настоящее время только компоновка в технологии MOSIS CMOS (mocmos) может быть проверена таким образом. Однако клавишей "Edit Dracula Deck" диалога DRC Options... задание правил может быть определено для любой технологии. |

|

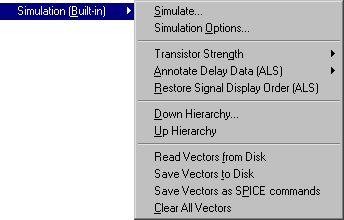

Это подменю управляет симулятором уровня вентиля (gate-level) в Electric. Electric приходит с симулятором, названным ALS (Asynchronous Logic Simulator), но вы можете также добавить IRSIM. Вы можете управлять симуляцией, перемещаясь вверх и вниз по иерархии, управлять векторами тестирования и устанавливать параметры симуляции. |

|

|

Simulate... |

Эта команда приводит к тому, что текущий фасет будет симулироваться. Если текущий фасет не netlist, и ассоциированный с этим фасетом netlist пропущен или не имеет данных, компилятор VHDL вызывается, чтобы построить новый. Если текущий фасет не VHDL, а VHDL, ассоциированный с этим фасетом пропущен или не имеет данных, он генерируется из схемы или компоновки. Дисплей отображения сигналов (waveform) обычно показывает значения наблюдаемых сигналов. |

|||||

|

|

Simulation Options... |

Эта команда предлагает диалог для управления параметрами симуляции. Движок симуляции может быть выбран (первоначально Electric приходит только с симулятором ALS, но встроенный IRSIM доступен на Static Free Software. Флажок "Resimulate each change" приводит к тому, что каждое изменение, сделанное для чего-то подлежащего симуляции, включает симуляцию заново и отображает результаты. Флажок "Auto advance time" говорит симулятору, что следует перемещать курсор автоматически, когда новый сигнал добавляется в симуляцию. Установка "Multistate display" говорит симулятору, что следует показать сигналы в окне компоновки или схемы с текстурой и цветом для отображения интенсивности. Без этого простой индикатор «on/off» нарисован в окне компоновки или схемы. Флажок "Show waveform window" говорит симулятору, что необходимо создать новое окно с отображением сигналов при старте симулятора. Окно сигналов может быть каскадировано (отдельным перекрывающим окном) или быть в виде мозаики (размещено в одной половине оригинального окна схемы). Основание базы сигналов в окне отображения сигналов может быть выбрано. Для ALS максимальное число событий симуляции может быть изменено, если вы хотите расширить пределы симуляции (и использования памяти). Может быть задан уровень паразитных параметров и файл этой информации для IRSIM.  |

|||||

|

|

|

|

|||||

|

|

Transistor Strength |

|

Эта команда позволяет вам изменить интенсивность выбранного транзистора. |

||||

|

|

Annotate Delay Data (ALS) |

|

Эта команда позволяет вам выбрать, какую из установок данных симуляции использовать симулятором ALS. Данные симуляции получаются с помощью субкоманды SDF команды Import меню File. |

||||

|

|

Restore Signal Display Order (ALS) |

Эта команда восстанавливает предопределенные установки сигналов в окне отображения сигналов, которые полезны, если они были переопределены или если некоторые сигналы были удалены. Команда работает только с ALS симулятором. |

|||||

|

|

|

|

|||||

|

|

Down Hierarchy... |

Эта команда приводит к тому, что симуляция опускается по иерархии к нижним уровням так, что сигналы могут быть наблюдаемы здесь. Вам будет предложен список нижних уровней для наблюдения. |

|||||

|

|

Up Hierarchy |

Эта команда приводит к тому, что симуляция поднимается к следующему верхнему уровню иерархии. |

|||||

|

|

|

|

|||||

|

|

Read Vectors from Disk |

Эта команда приводит к тому, что файл векторов тестирования будет прочитан с диска. Вам будет предложено ввести имя файла. |

|||||

|

|

Save Vectors to Disk |

Эта команда приводит к тому, что текущие установки векторов тестирования будут сохранены на диске. Вам будет предложено ввести имя файла. |

|||||

|

|

Save Fectors as SPICE commands |

Эта команда экспортирует текущие установки векторов тестирования, как деку SPICE. |

|||||

|

|

Clear All Vectors |

Эта команда очищает все векторы тестирования из симуляции. |

|||||

|

|

Это подменю управляет симулятором SPICE, включая генератор деки и черчение вывода SPICE. |

|

|

Write SPICE Deck |

Эта команда генерирует входную деку для SPICE уровня схемы симулятора. Поскольку SPICE не интерактивная система, необходимо обозначить вход и выход в схеме. Это выполняется размещением компонент Source и Meter (из подменю New Analog Component меню Edit), параметризуя их актуальными сообщениями SPICE, и присоединяя их к схеме. Также необходимо обозначить Transient или DC анализ размещением подходящих компонент Source в фасете. |

|

|

SPICE Options... |

Эта команда позволяет управлять многими опциями SPICE, например, форматом SPICE (SPICE 2, SPICE 3, HSPICE или PSPICE); управлять паразитными параметрами в деке; управлять выполнением SPICE (только для системы UNIX); управлять заголовком, дополнением и индивидуальными карточками модели фасета; и много больше.

|

|

|

Plot SPICE Listing |

Эта команда читает вывод запущенного SPICE и показывает сигналы в окне отображения сигналов. |

|

|

Add SPICE Card |

Эта команда позволяет вам щелкнуть по разработке и ввести карточку SPICE, которая будет вставлена в сгенерированную деку. |

|

|

Set SPICE Template |

Эта команда позволяет вам создать шаблон SPICE при определении новых примитивов. |

|

|

Set SPICE Model... |

Эта команда позволяет вам изменить модель SPICE текущего выделенного узла. |

|

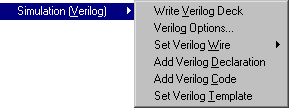

Это подменю управляет генерацией Verilog netlist симуляции. |

|

|

Write Verilog Deck |

Эта команда генерирует входную деку для симулятора Verilog. |

|

|

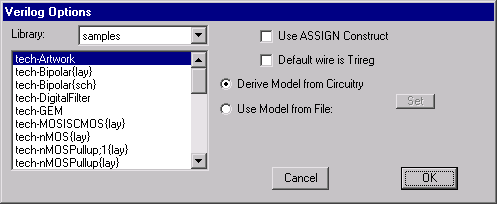

Verilog Options... |

Эта команда определяет вид диалога для управлением генерацией деки Verilog.  |

|

|

Set Verilog Wire |

Команда позволяет вам установить тип проводников Verilog, которые будет производить текущая дуга (либо Wire, Trireg или Default). Опция Default использует установки из диалога Verilog Options... |

|

|

Add Verilog Declaration |

Эта команда позволяет вам щелкнуть по разработке и ввести объявление Verilog, которое будет вставлено в сгенерированную деку. |

|

|

Add Verilog Code |

Эта команда позволяет вам щелкнуть по разработке и ввести код Verilog, который будет вставлен в сгенерированную деку. |

|

|

Set Verilog Template |

Эта команда позволяет вам создать шаблон Verilog, когда определяются новые примитивы. |

|

|

Это подменю позволяет входным декам записываться для многих разных симуляторов. |

|

|

FastHenry Arc Info... |

Эта команда открывает диалог для включения текущей выделенной дуги в анализатор FastHenry и для установки опций на этой дуге. Вы можете перезаписать толщину, установить количество подделений, установить группу анализа и даже установить высоту для двух концов дуги. |

|

||

|

|

Write FastHenry Deck... |

Команда генерирует деку FastHenry из текущего фасета. |

|||

|

|

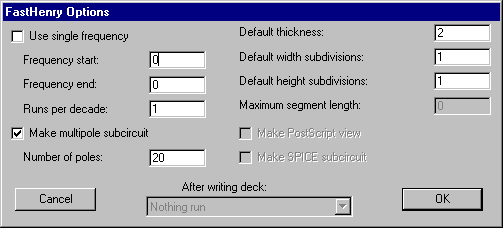

FastHenry Options... |

Команда представляет диалог опций для генерации деки FastHenry. Частота и многополюсные опции управляют флагами, которые размещаются в деке. Предопределенная толщина и поля подделений предоставляют значения, которые используются, когда не определено переписывания для отдельных дуг.  |

|||

|

|

|

|

|||

|

|

Write IRSIM Deck |

Эта команда генерирует входную деку для IRSIM симулятора уровня переключения. |

|||

|

|

Write ESIM Deck |

Эта команда генерирует входную деку для ESIM симулятора уровня переключения (nMOS только, без выбора времени). |

|||

|

|

Write RSIM Deck |

Эта команда генерирует входную деку для RSIM симулятора уровня переключения (nMOS только). |

|||

|

|

Write RNL Deck |

Эта команда генерирует входную деку для RNL симулятора уровня переключения (nMOS только, Lisp-подобный интерфейс). |

|||

|

|

Write COSMOS Deck |

Эта команда генерирует входную деку для COSMOS симулятора уровня переключения (MOS только). |

|||

|

|

Write MOSSIM Deck |

Эта команда генерирует входную деку для MOSSIM симулятора уровня переключения (MOS только). |

|||

|

|

|

|

|||

|

|

Write TEGAS Deck |

Эта команда генерирует входную деку для TEGAS/TEXSIM симулятора уровня вентиля (gate-level). |

|||

|

|

Write SILOS Deck |

Эта команда генерирует входную деку для симулятора SILOS. |

|||

|

|

Write PAL Deck |

Эта команда генерирует входную деку для генератора/симулятора Abel PAL. |

|||

|

|

Эти команды выполняют статический анализ цепи, который в настоящее время только анализатор карманов. |

|

|

Analyze Wells |

Эта команда проверяет текущий фасет и все области кармана на выполнение электрических правил. Показано самое дальнее расстояние от контакта кармана до края его имплантанта. |

|

|

ERC Options... |

Это предоставляет диалог с опциями Electric Rules Checking. Для областей нижнего слоя и карманов вы можете выбрать, затребовать один контакт на область или только один контакт в любом месте чипа. Вы также можете проверить правильность соединений питания и земли.

|

|

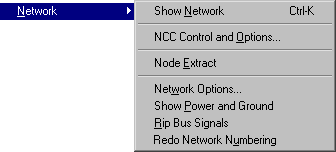

Это подменю управляет смешанными функциями сетей, включая возможность Network Consistency Checking (NCC). Некоторые системы называют проверку правильности сети "LVS" (Layout vs. Schematic), но Electric использует термин NCC, поскольку он может сравнить любые два фасета, а не только layout vs. schematic. |

|

|

Show Network |

Эта команда показывает текущие подсвеченные сети во всех других окнах. Она также работает с именами сетей выбранными в текстовом окне. Если фасет пропущен через контролер правильности сети, эта информация будет использоваться. |

|||

|

|

|

|

|||

|

|

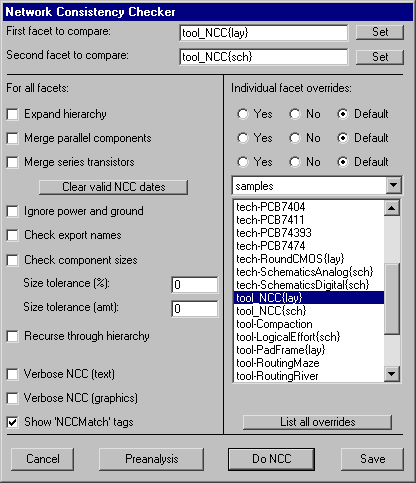

NCC Control and Options... |

Это предоставляет диалог для управления контролером правильности сети. Наверху есть два фасета, чьи сети должны сравниваться. Если есть два фасета для текущего отображения, они загружаются в эти поля.  Нижняя часть управляет процессом NCC. Слева управление NCC, а в правой половине пофасетная замена некоторых из этих установок. Нижняя часть имеет клавиши для запуска NCC или Preanalysis. |

|||

|

|

|

|

|||

|

|

Node Extract [7-3] |

Эта команда извлекает связность из фасета, который имеет только геометрию (узлы чисто уровня). Такие фасеты – результат чтения внешних форматов, таких как CIF и GDS. Узлы чисто уровня удаляются и замещаются присоединенной сетью узлов и дуг. К сожалению, экстрактор узлов ранней разработки и не был рассчитан на правильное извлечение. Также он не распознает транзисторы в настоящее время. |

|||

|

|

|

|

|||

|

|

Network Options... |

Этим открывается диалог для управления инструментами сети. Верхняя часть управляет опциями нумерации сети. |

|||

|

"Unify Power and Ground" показывает, что все порты питания и земли должны считаться электрически связанными, не зависимо от их связности в схеме. Сброс флажка может быть только в schematics, где появляются узлы Power и Ground. "Unify all like-named nets" показывает, что все сети с одинаковыми именами должны быть объединены, независимо от природы сети. Сброс флажка характерен только для фасет схем (schematic), имеющих электрически соединенные и схоже именованные сети. |

|

||||

|

Нижняя часть диалога управляет тем, как будут нумероваться шины, когда они явно не определены. Вы можете выбрать, начинать ли их с 0 или 1, и можете выбрать порядок возрастания и убывания. |

|||||

|

|

Show Power and Ground |

Эта команда подсвечивает все сети питания и земли в текущем фасете. |

|||

|

|

Rip Bus Signals [7-6] |

Эта команда берет текущие выделенные провода шины и добавляет ответвления проводов для каждого сигнала шины. Провода идут перпендикулярно шине и маркированы их сигналами. |

|||

|

|

Redo Network Numbering [6-12] |

Команда, в основном, не нужна, но может быть полезна, если вы подозреваете, что информация сети некорректна. |

|||

|

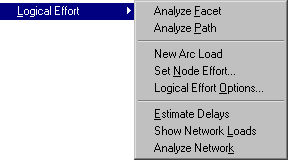

Эта команда осуществляет Logical Effort анализ, определяющий пропорции транзисторов, используемые в компонентах цифровых схем, в плане получения оптимальной скорости цепи. |

|

|

Analyze Facet |

Команда проверяет текущий фасет и аннотирует все вентили схемы информацией об источниках сигналов. |

|||

|

|

Analyze Path |

Эта команда проверяет цепь между двумя подсвеченными компонентами и аннотирует вентили информацией об источниках сигналов. |

|||

|

|

|

|

|||

|

|

New Arc Load |

Команда создает специальный символ нагрузки ("load"), который имеет емкость и может соединяться с цепью для объявления здесь нагрузки. Значение емкости может быть изменено двойным щелчком и вводом нового значения. |

|||

|

|

Set Node Effort... |

Эта команда позволяет вам установить перезаписываемое значение логического напряжения (logical effort) на текущем выделенном узле. Это значение может быть изменено двойным щелчком и вводом нового значения. |

|||

|

|

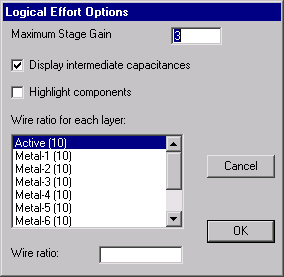

Logical Effort Options... |

Эта команда предоставляет опции для управления инструментом Logical Effort. |

|||

|

Maximum Stage Gain используется командой Analyze Facet. "Display intermediate capacitances" позволяет отображать значение емкости на дуге в цепи. "Highlight components" приводит к тому, что инструмент подсвечивает активные компоненты, которые анализируются. |

|

||||

|

И, наконец, диалог позволяет вам установить пропорции проводников для каждой дуги (значение используется в расчетах нагрузки). |

|||||

|

|

|

|

|||

|

|

Estimate Delays |

Эта команда проверяет каждую сеть в схеме и вычисляет факторы нагрузки. Обычно она бесполезна, и относится к вычислениям Logical Effort. |

|||

|

|

Show Network Loads |

Эта команда выводит список каждой сети в текущем фасете, показывая длину проводника, нагрузку и другую информацию. |

|||

|

|

Analyze Network |

Эта команда показывает детальный анализ текущей выделенной сети, включая информацию о площади и периметре каждого слоя, и информацию о нагрузке. |

|||

|

|

Это подменю управляет количеством возможных трассировок проводников. |

|

|

Enable Auto-Stitching |

Команда инструктирует трассировщик просмотреть всю последующую активность компоновки и разместить дуги, где бы касающиеся узлы ни создавали потенциальные соединения. Полезно вызвать эту команду перед генерацией массивов, поскольку массивы могут производить много потенциальных соединений, которые этот трассировщик будет делать явными. Пункт меню изменяется на Stop Auto-Stitching для выключения этой функции. |

|||

|

|

Auto-Stitch Highlighted Now |

Это дает автоформирование соединений (auto-stitching) только в текущей подсвеченной области. Подсвеченная область определена, как ограниченный прямоугольник всего, что подсвечено. Более точный метод определения подсвеченной области – использовать клавишу rectangle select для растягивания прямоугольника по экрану. |

|||

|

|

|

|

|||

|

|

Enable Mimic-Stitching |

Эта команда инструктирует трассировщик просмотреть всю последующую активность компоновки и автоматически создать другие дуги в похожих местах, где бы они не были созданы вручную. Пункт меню меняется на Disable Mimic-Stitching для выключения этой функции. |

|||

|

|

Mimic-Stitching Now |

Эта команда инструктирует трассировщик имитировать последнюю дугу, которая была создана. Это не обязательно для работы Mimic Stitcher. |

|||

|

|

|

|

|||

|

|

Maze-Route Selected |

Эта команда запускает лабиринтный трассировщик (maze router) в выделенной области. Все обнаруженные Unrouted проводники будут замещены реальной геометрией. |

|||

|

|

Maze-Route Facet |

Эта команда запускает лабиринтный трассировщик в текущем фасете. Все обнаруженные Unrouted проводники будут замещены реальной геометрией. |

|||

|

|

|

|

|||

|

|

River-Route |

Эта команда запускает потоковый трассировщик (river-router) в текущем фасете. Все обнаруженные Unrouted проводники будут замещены реальной геометрией. |

|||

|

|

|

|

|||

|

|

Routing Options... |

Эта команда предоставляет диалог управления стежковых трассировщиков (stitching routers). |

|||

|

Для автоформирования соединений (Auto-Stitcher) вы можете выбрать тип применяемой дуги (по умолчанию автоматическое определение типа дуги по портам). |

|

||||

|

Для Mimic-Stitcher вы можете инструктировать его имитировать удаление проводников, как и их создание. Mimic-Stitcher может также быть проинструктирован на ослабление правил имитации (по умолчанию дуги имитируются, если они проходят между одинаковыми портами на других узлах; однако вы можете запросить, чтобы имитация происходила между любыми другими портами, имеющими такие же промежутки, что и оригинальная дуга). |

|||||

|

|

|

|

|||

|

|

Unroute |

Эта команда берет текущую подсвеченную сеть (сети) и конвертирует их в неразведенные проводники (unrouted wires). После этой команды вы может использовать maze-route или river-route неразведенных проводников. |

|||

|

|

Get Unrouted Wire |

Unrouted wire технологии Generic используется для определения требований трассировки (см. раздел 7-9). Эта команда выделяет Generic дугу так, что последующие команды разводки будут ее использовать. Это необходимо в плане выполнения maze и river-routing. |

|||

|

|

Copy Routing Topology |

Команда запоминает сеть соединений в текущем фасете для последующего создания в другом фасете (определенном с помощью Paste Routing Topology). |

|||

|

|

Paste Routing Topology |

Команда проверяет текущий фасет и сравнивает его сеть с той, что была скопирована (командой Copy Routing Topology). Там, где есть пропущенные соединения в этом фасете, команда создает Unrouted дуги для их соединения. |

|||

|

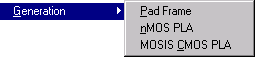

Эта команда предоставляет генератор pad frame и два PLA генератора. Все будет работать быстрее, если вначале выключить контролер правил разработки. |

|

|

Pad Frame [9-8] |

Эта команда запросит дисковый файл, который описывает размещение площадок вокруг ядра фасета. Файл включает информацию о библиотеке, которая содержит площадки и также соединения между площадками и портами на ядре фасета. |

|

|

nMOS PLA [9-7] |

Команда запросит персональные таблицы и сгенерированную nMOS компоновку, укомплектованную питанием и тактовыми сигналами. Смотрите описание генератора PLA с примером персональной таблицы. |

|

|

MOSIS CMOS PLA [9-7] |

Эта команда запрашивает две персональные таблицы: AND и OR таблицы. Также предлагаются опции, касающиеся положения входов и выходов. Смотрите описание генератора PLA с примером CMOS персональной таблицы. |

|

|

Это подменю предоставляет прямое управление компилятором VHDL, который транслирует VHDL тестовое описание в netlist. Перед заданием формата генерируемого netlist возможно также определить, будет ли netlist VHDL сохранен в памяти (в фасете) или на диске. |

|

|

Compile for Silicon Compiler |

Эта команда приводит к тому, что VHDL в текущем фасете будет компилироваться в netlist для компилятора silicon. Если текущий фасет не вида VHDL, используется вид VHDL. Если дисковый файл VHDL используется вместо фасет, прочитывается файл "XXX.vhdl", где XXX – это имя ячейки текущего фасета. Если netlist записывается на диск, записывается файл "XXX.sci". |

|||

|

|

Compile for Simulation |

Эта команда приводит к тому, что VHDL в текущем фасете компилируется в netlist для симуляции. Если текущий фасеты не вида VHDL, используется вид VHDL. Если вместо фасет используются дисковые файлы VHDL, читается файл "XXX.vhdl", где XXX – имя ячейки текущего фасета. Если netlist записывается на диск, записывается файл "XXX.net". |

|||

|

|

Compile for RNL |

Эта команда приводит к тому, что VHDL в текущем фасете компилируется в netlist симулятора RNL. Если текущий фасет не вида VHDL, используется вид VHDL. Если используются дисковые файлы VHDL вместо фасет, прочитывается файл "XXX.vhdl", где XXX – имя ячейки текущего фасета. Если netlist записывается на диск, записывается файл "XXX.net". |

|||

|

|

Compile for RSIM |

Эта команда приводит к тому, что VHDL в текущем фасете компилируется в netlist симулятора RSIM. Если текущий фасет не вида VHDL, используется вид VHDL. Если используются дисковые файлы VHDL вместо фасет, прочитывается файл "XXX.vhdl", где XXX – имя ячейки текущего фасета. Если netlist записывается на диск, записывается файл "XXX.net". |

|||

|

|

Compile for SILOS |

Эта команда приводит к тому, что VHDL в текущем фасете компилируется в netlist симулятора SILOS. Если текущий фасет не вида VHDL, используется вид VHDL. Если используются дисковые файлы VHDL вместо фасет, прочитывается файл "XXX.vhdl", где XXX – имя ячейки текущего фасета. Если netlist записывается на диск, записывается файл "XXX.sil". |

|||

|

|

|

|

|||

|

|

VHDL Options... |

Эта команда предоставляет опции управления того, что будет ли VHDL или Netlist сохраняться в памяти или на диске. Помимо субкоманд компиляции в этом меню состояние этих переключений сказываются также на команде Make VHDL View меню View, субкоманде Simulate... команды Simulation (Built-in) меню Tools и субкоманде Get Network for Current Facet команды Silicon Compiler меню Tools. |

|

||

|

Эта команда также управляет VHDL, генерируемым из узлов schematics. Каждый узел схемы показан с его регулярными или инверсными символами VHDL (использование "%d" замещается номером входа на вентиле). |

|||||

|

|

Select Behavioral Library... |

При компиляции для симуляции поведение моделей будет отображаться, если они найдены в текущей библиотеке. Эта команда позволяет искать модели в альтернативной библиотеке. Заметьте, что каждая модель может быть найдена в "netlist-als-format" виде соответственно названной ячейки. |

|||

|

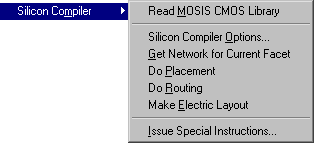

Это подменю – это обширная система для размещения и трассировки библиотек стандартных ячеек из структурированного описания VHDL. Просто запустите каждую команду в последовательности: выбрать библиотеку, установить опции, получить netlist, разместить, развести и сделать Electric компоновку. |

|

|

Read MOSIS CMOS Library |

Эта команда требует, чтобы MOSIS CMOS стандартная библиотека ячейки была использована. Эта библиотека ячейки не гарантирует правильности и существует только для иллюстративных целей. Смотрите раздел "Silicon Compiler" Части 9, где описаны все ячейки этой библиотеки. |

|

|

|

|

|

|

Silicon Compiler Options... |

Команда открывает диалог, позволяющий установить различные параметры процесса silicon компиляции. |

|

|

Get Network for Current Facet |

Эта команда берет netlist для текущего фасета. Если текущий фасет не netlist, и netlist, ассоциированный с этим фасетом пропущен или не имеет данных, VHDL Compiler будет использован для создания netlist. Если текущий фасет не VHDL, и ассоциированный с этим фасетом VHDL пропущен или не имеет данных, VHDL будет сгенерирован из schematic. |

|

|

Do Placement |

Эта команда вычисляет размещение стандартных ячеек. |

|

|

Do Routing |

Эта команда вычисляет трассировку между размещенными стандартными ячейками. |

|

|

Make Electric Layout |

Эта команда генерирует конечную схему из вычисленных размещения и трассировки. Контролер правил разработки выключен на этом шаге. |

|

|

|

|

|

|

Issue Special Instructions... |

Эта команда позволяет вам общаться напрямую с Silicon Compiler. Только те, кто хорошо знаком с системой могут воспользоваться этим (другие команды в этом подменю поддерживают стандартные функции без необходимости знать, как работает компилятор). |

|

Это подменю управляет компактором компоновки. |

|

|

Do Compaction |

Эта команда сжимает компоновку в текущем окне к расстоянию правил разработки, используя сжатие по одной оси. Разделяется горизонтальное и вертикальное сжатие пока не может быть сохранено дополнительное пространство. Сжатие выполняется нисходящим и влево. |

|||

|

|

Compact Horizontally |

Команда инструктирует компактор сжимать текущий фасет только один раз в горизонтальном направлении. |

|||

|

|

Compact Vertically |

Команда инструктирует компактор сжимать текущий фасет только один раз в вертикальном направлении. |

|||

|

|

Compaction Options... |

Эта команда открывает диалог, позволяющий вам сказать компактору, что нужно растянуть цепь, где она слишком плотна по правилам разработки. Вы можете также запросить информацию о процессе уплотнения. |

|

||

Эта команда выводит список всех инструментов, показывая, какие из них активны.

|

|

В Electric есть интерпретаторы языков: TCL, LISP и Java. Интерпретаторы могут активироваться субкомандами здесь. После активизации вы общаетесь с ними окне сообщений. Заметьте, что из-за ограничений прав копирования интерпретаторы TCL и LISP не являются частью стандартного GNU дистрибутива и должны быть получены отдельно с Static Free Software. Интерпретатор Java также должен быть получен отдельно (см. инструкции по установке для UNIX, раздел 1-3, и Windows, раздел 1-5). |

|

|

|