9-2: Проверка правил разработки |

Часть 9: ИНСТРУМЕНТЫ

9-2: Проверка правил разработки |

Программа проверки правил разработки

(design-rule checker) - это коллекция средств для

проверки размещения схемы. По умолчанию

есть инкрементный (incremental ) инструмент

проверки правил, который наблюдает за

работой на протяжении сессии и выводит

сообщения об ошибках, если геометрия

некорректна. Иерархический контролер

(hierarchical checker) проверяет компоновку

иерархически. Вдобавок, можно подготовить

деку (deck - в данном случае файл,

состоящий из набора текстовых карточек,

необходимых программе) ввода для Dracula,

внешнего контролера правил разработки.

Инкрементный контролер правил разработки всегда запущен, проверяя вашу работу и выводя сообщения об ошибках, если последние обнаруживаются. Контролер обнаруживает три типа ошибок. Ошибки расположения (Spacing) вызываются геометрией, когда она слишком закрыта, но не соединена. Ошибки меток (Notch) вызываются геометрией, когда она слишком закрыта, но соединена. Ошибки минимального размера (Minimum size) вызываются геометрией, когда она слишком мала.

В дополнение к проверке геометрии контролер правил разработки использует информацию связности, чтобы помочь найти нарушения. Используется информация сети для помощи разработчику в отладке связности цепи. Например, если два перекрывающихся узла не соединены дугой, они могут считаться нарушенными, даже если их геометрия выглядит правильно. Происходит это благодаря тому, что контролер знает о соединениях, и имеет отдельный набор правил для таких ситуаций.

Пользователю следует знать, что инкрементный контролер правил разработки не проверяет иерархию. Это означает, что если в цепи используется образец фасета, контролер правил разработки не проверяет его содержание, чтобы увидеть взаимодействие с другими слоями, обрамляющими образец. Для проверки полной иерархии используйте субкоманду Hierarchical Check.

Для управления DRC и установки правил используйте субкоманду DRC Options... команды DRC меню Tools.

По умолчанию инкрементный контролер правил разработки включен. Для его выключения снимите флажок "On" в секции "Incremental DRC". Пока инструмент выключен Electric сохраняет отслеживание всех фасет, которые изменяются. Когда инструмент вновь включается, он перепроверяет все эти изменения. Таким образом, контролер правил разработки может быть организован в пакетный ("batch") инструмент с поддержанием его выключенным, пока компоновка цепи не будет завершена.

|

|

|

Инкрементная программа проверки правил разработки имеет два стиля, в которых работает. По определению, каждое нарушение просто отображается в окне сообщений, при этом не предполагается подтверждений. Если вы установите флажок "Highlights errors" в диалоге, следствием станет подсветка нарушений, а система будет ожидать дальнейших инструкций. Снимите флажок, чтобы выключить этот интерактивный режим.

|

|

Когда интерактивный режим включен, при обнаружении любых нарушений правил разработки будет появляться диалог. Возможная реакция на появление этого диалога - продолжение проверки (клавиша "OK"), запоминание этого нарушения и игнорирование при последующей проверке (клавиша "Ignore this error"), продолжение проверки молча (клавиша "Continue Silently") и прерывание проверки (клавиша "Stop Checking"). |

Клавиши "Continue Silently (продолжить молча)" и "Stop Checking (прекратить проверку)" могут обращаться к текущему пакету ошибок ("For now (сейчас)") или постоянно (это влияет на установку в диалоге "DRC Options"). Ошибки, которые игнорируются, запоминаются и больше никогда не выводятся. Чтобы очистить список таких проигнорированных ошибок используйте субкоманду Clear Ignored Errors.

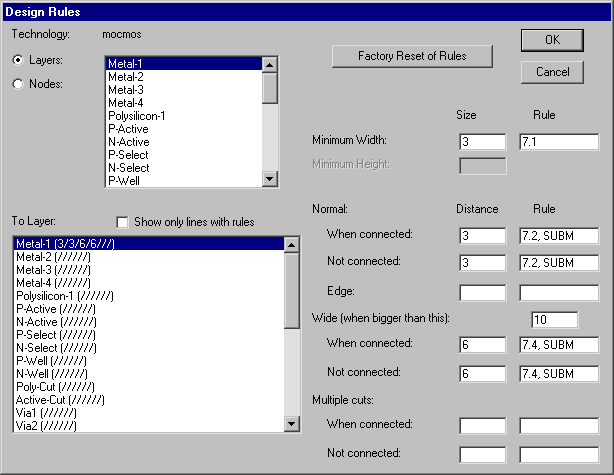

Диалог DRC Rules... позволяет вам проверить и модифицировать ограничения интервалов для текущей технологии. Вы можете выбрать "Layers" или "Nodes". При выборе "Nodes" вы можете установить минимальные размеры каждого узла в текущей технологии.

Когда выбрано "Layers", вы можете установить минимальные размеры каждого слоя, а кроме того внутрислойные интервалы (между данным и "To Layer"). Используйте "Show only lines with rules (показать только линии с правилами)" для ограничения показа правил теми, что имеют обоснованные значения. Каждое правило интервалов приходит с системой в двух вариантах: «соединенное и не соединенное». «Соединенное» правило обращено к двум разным слоям, которые электрически соединены; не соединенное - к не соединенным слоям. Специальное правило Edge обращено только к не присоединенным слоям и игнорирует перекрытие, когда просматривается величина интервалов. «Соединенное и не соединенное» (connected и unconnected) правила приходят с системой в трех стилях: «нормальный, широкий и множественные вырезы». «Широкие» правила подходят, когда слой шире, чем специфицированная величина. Правила «множественных вырезов» подходят, когда слой - часть многовырезного контакта. В дополнение к обозначенным интервалам, вы можете дать описание правила, которое будет сообщаться контролером проверки правил. Клавиша "Factory Reset of Rules" переустановит все правила к оригинальному виду, встроенному в Electric.

После вывода сообщений об ошибках вы можете просматривать их, вводя ">" и "<", чтобы перешагивать к следующей и предыдущей ошибкам, которые были найдены. Если вы хотите перепроверить весь фасет, используйте субкоманду Check this Level Only (проверить только этот уровень).

Заметьте, что правила разработки MOSIS CMOS 6.7b не проверяются Electric, поскольку ошибки трудно обнаружить корректно. Эти ошибки никогда не бывают фатальными, и самое плохое, что произойдет, если ошибку пропустить, это то, что активный и поликристаллический слои сблизятся больше, чем на 1/2 лямбда, что скажется только на увеличении емкостной связи между ними. Если эта дополнительная емкость важна, вы, возможно, получили так много поликремния в вашей цепи, что это гораздо большая проблема.

Иерархический контролер правил разработки использует те же правила и технологии, что и инкрементный, но способен проверять все уровни иерархии. Для его запуска используйте субкоманду Hierarchical Check команды DRC меню Tools.

После анализа схемы вы можете просмотреть ошибки, вводя ">" и "<" для перешагивания к следующей или предыдущей ошибке, которые были обнаружены.

После того, как прохождение иерархического DRC по фасету не обнаруживает ошибок, он помечается текущей датой. При следующем запуске иерархического DRC, если фасет не модифицировался после этой даты, он не перепроверяется. (Однако, если вы изменили правила DRC или опции технологии, вся информация о дате очищается). Если вы хотите форсировать перепроверку всех фасет, используйте клавишу "Clear valid DRC dates (очистить правильные даты DRC)" в диалоге DRC Options... Чтобы увидеть, какой фасет прошел проверку иерархическим DRC, используйте команду Feneral Facet Lists... меню Facets ("D" справа от фасета показывает текущий DRC).

Другой способ ускорить работу иерархического DRC - установить "Just 1 error per facet (только 1 ошибка на фасет)" флажок в диалоге DRC Options... Этим системе сообщается, что следует остановить проверку фасета после обнаружения первой ошибки. Используя эту опцию, вы можете гораздо быстрее определить, какие фасеты в разработке не имеют ошибок, без уточнения места ошибки. Затем вы можете перейти к фасету с ошибками и провести комплексную проверку.

Если вы счастливчик, имеющий компьютер с более, чем одним процессором, DRC может использовать это преимущество при выполнении иерархической проверки. Установите флажок "Use multiple processors (использовать многопроцессорный режим)" в диалоге DRC Options... и укажите, сколько процессоров использовать. Значение в этом поле производит много параллельных процессов для выполнения DRC, так что значение может быть больше, чем количество процессоров. Текущий алгоритм использует раздельные процессы для анализа каждого субобразца в фасете. Следовательно, фасеты с множеством субобразцов покажут лучшую скорость с этой опцией.

Если установлено "Use dialog (использовать диалог)" в секции "Hierarchical DRC" диалога DRC Options..., тогда будет появляться диалог при выполнении иерархической DRC.

|

Выберите клавишу "Check" для начала проверки. Когда проверка закончена, вы можете увидеть ошибки с помощью клавиш "Show Next Error" и "Show Prev Error". Используйте клавишу "Done" для прекращения проверки. |

|

Еще одна возможность проверки правил разработки, которая доступна в Electric, это интерфейс с Dracula контролером правил разработки. Этот интерфейс требует описания цепи и набора правил разработки. Electric знает правила разработки (в данный момент только для технологии MOSIS CMOS) и способен генерировать правильное описание цепи (CIF файл). Для генерации этого файла используйте субкоманду Write Dracula Deck.

Чтобы увидеть набор правил разработки Dracula для текущей технологии, используйте клавишу "Edit Dracula Deck" субкоманды DRC Options... Это отобразит правила в окне редактирования. Правила должны содержать строки: "PRIMARY =" и "INDISK = " с тем, чтобы дек-генератор мог заменить правильные имена файлов.

Заметьте, что только технология "mocmos" имеет подходящие правила разработки, так что эта команда выведет пустое окно, когда запускаются другие технологии. Однако вы можете создать ваши собственные правила разработки для любой технологии. Чтобы это сделать, выполните следующие шаги:

Используйте команду Change Current Technology... из меню Technology для переключения к технологии "mocmos".

Отредактируйте правила, используя эту команду.

Выберите все и используйте команду Copy меню Edit для их копирования.

Закройте окно редактирования текста.

Используйте команду Change Current Technology... меню Technology для переключения на желаемую технологию.

Отредактируйте правила с этой командой, которая отображает чистое окно редактирования.

Используйте команду Paste меню Edit для перезаписи правил MOSIS CMOS.

Теперь вы можете редактировать эти правила, и они будут сохранены с вашими опциями.

Для помощи в работе с контролером Dracula может быть размещен слой "cloaking (маски)" поверх пространства, которое не подлежит проверке. Этот слой маски создается использованием субкоманды DRC Exclusion команды New Special Object меню Edit. Узел, который помещается, производит слой названный "DRC" в файле Dracula, который приводит к тому, что схема под ним будет игнорироваться.

|

|

|